1. Kondisi [kembali]

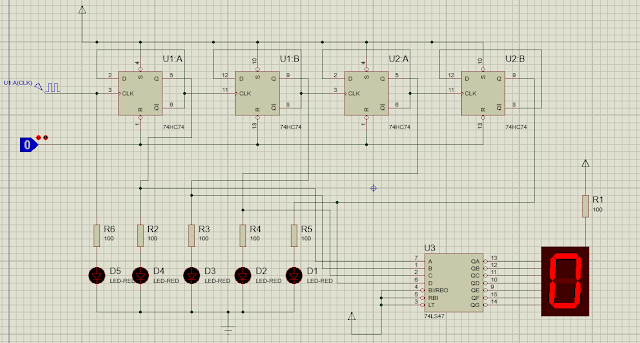

Buatlah rangkaian seperti gambar percobaan 1 menggunakan D Flip flop dan output seven segment.

2. Komponen [kembali]

a. IC 74HC74

b. Seven Segment

c. VCC

d. BCD 74LS47

e. LED

f. Logicstate

g. Resistor

h. Ground

i. Clock

a. IC 74HC74

b. Seven Segment

c. VCC

d. BCD 74LS47

e. LED

f. Logicstate

g. Resistor

h. Ground

i. Clock

3. Rangkaian Simulasi [kembali]

4. Prinsip kerja rangkaian [kembali]

D flip-flop merupakan pengembangan dari SR Flip-flop. Kedua masukan input SR flip flop dimodifikasi dengan

menambahkan inverter sehingga D flip flop hanya memiliki satu input saja.

Rangkaian diatas merupakan 4-bit asynchronous (ripple) up counter counter

menggunakan 74HC74 D flip flop,yang mana input clock flip flop pertama dari function generator dan input flip flop berikutnya berasal dari output flip flop pertama dan seterusnya.

Saat Logicstate berlogika 0, maka output akan selalu menunjukkan angka 0. karena pada CLR (RESET) merupakan active LOW.

Saat Logicstate berlogika 1, maka output akan mencacah dari 0000 hingga 1111 secara berulang-ulang.

Output dari flip-flop dihubungkan ke BCD 74LS47 sebelum dihubungkan ke seven segment common anode, berfungsi sebagai decoder agar output biner dapat terbaca.

Output dari rangkaian akan terlihat sebagai berikut (berdasarkan datasheet BCD 74LS47) :

Tidak ada komentar:

Posting Komentar